# Fairchild Imaging CIS 2521F Standard and Scientific Package Datasheet

# 5.5 Megapixel CMOS Image Sensor

For the latest data sheet, please visit www.sunnywale.com

PRODUCT DESCRIPTION (Rev : E)

The Fairchild Imaging CIS2521F is a large format, ultra low-noise CMOS image sensor intended for scientific and industrial applications requiring high quality imaging under extremely low light conditions. The device features an array of 5 transistor (5T) pixels on a 6.5µm pitch with an active imaging area of 2560(H) x 2160(V) pixels. The sensor runs in Rolling Shutter and Global Shutter readout modes. The sensor has two ADC channels per column with one optimized for very low light levels and the other optimized for high light levels, allowing high dynamic range data collection in a single image. The sensor supports user-programmable row start/stop control for region of interest (ROI) readout mode. The CIS2521F delivers extreme low-light sensitivity with a read noise less than 2

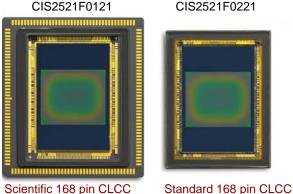

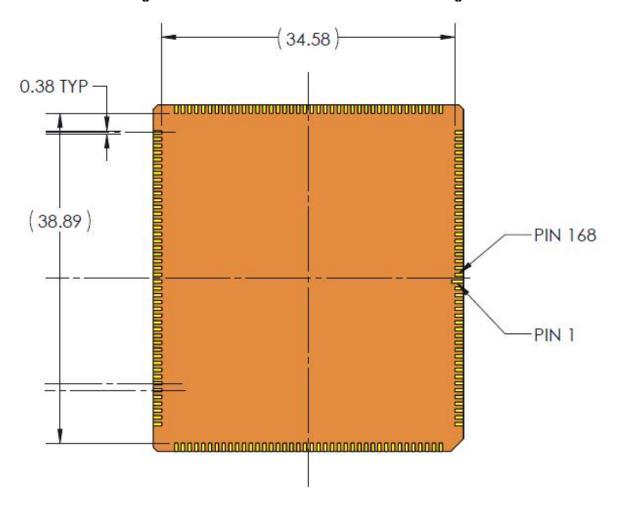

Scientific 168 pin CLCC

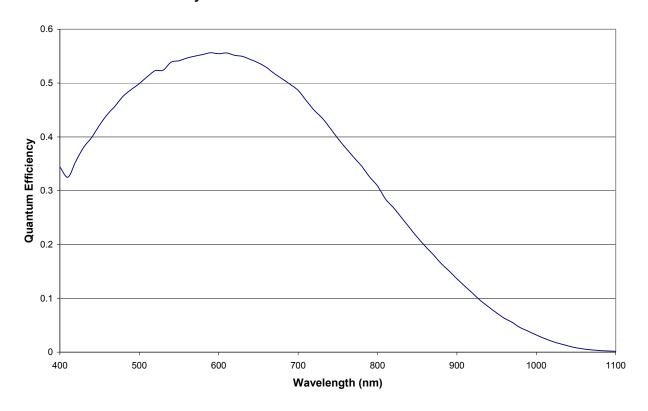

electrons RMS, Quantum Efficiency (QE) above 55%, and very low dark current. These features, combined with 5.5 megapixel resolution and 100 fps imaging rates, make the CIS2521F an imaging device ideally suited for a variety of high throughput, low light-level imaging applications.

The CIS2521F sensor is available in a 168 pin Scientific package (CIS2521Fx121), or in a 168 pin Standard package (CIS2521Fx221). For this datasheet, both packaged options are specified. The Scientific package is shown above on the left and the Standard package is shown above on the right.

| FEATURES                                                                                              | BENEFITS                                       |  |  |

|-------------------------------------------------------------------------------------------------------|------------------------------------------------|--|--|

| 2560 (H) x 2160 (V) pixel CMOS Image Sensor                                                           | 5.5 Megapixels of data                         |  |  |

| 6.5 μm x 6.5 μm pixel area                                                                            | Ideal pixel size for maximum light collection  |  |  |

| Maximum frame rates: -100 fps in Rolling Shutter readout mode - 50 fps in Global Shutter readout mode | Precise capture of dynamic events              |  |  |

| < 2 e- RMS Readout Noise                                                                              | Enables ultra low-light imaging                |  |  |

| Programmable ROI readout                                                                              | Flexible windowing to allow faster frame rates |  |  |

| < 35 e-/pixel/sec dark current @ 20°C                                                                 | Cooling not required for dynamic applications  |  |  |

| ≥ 55% peak Quantum Efficiency (QE)                                                                    | High sensitivity from visible through NIR      |  |  |

| > 83.5 dB intra-scene dynamic range                                                                   | Record intense & faint features simultaneously |  |  |

| On-chip column parallel 11-bit A/D converters  Dual gain 11-bit output channels per pixel             | Digital sensor for more compact designs        |  |  |

# **Table of Contents**

| Sensor naming convention                                       |    |

|----------------------------------------------------------------|----|

| General Specifications                                         | 5  |

| Electrical-optical specifications                              |    |

| Recommended Operating Conditions                               |    |

| Timing Specifications                                          |    |

| JTAG Interface                                                 |    |

| Functional Control Inputs                                      |    |

| Data and Status Outputs                                        |    |

| Device Architecture                                            |    |

| Sensor Floor plan                                              |    |

| Sensor Architecture                                            |    |

| Pixel architecture                                             |    |

| Column readout circuitry                                       |    |

| Sensor Data                                                    |    |

| Sensor Interface                                               |    |

| JTAG Interface                                                 |    |

| Control Signals                                                |    |

| Global Shutter Readout Mode Pixel Control                      |    |

| Power up sequence                                              |    |

| Power down sequence                                            |    |

| Selective component power down                                 |    |

| Readout Modes                                                  |    |

| Region of Interest                                             |    |

| Rolling Shutter readout                                        |    |

| Seamless change of integration time in Rolling Shutter readout |    |

| Pseudo single port readout mode                                |    |

| Global Shutter                                                 |    |

| Pause/Resume using READ pin                                    |    |

| Reset using READ pin                                           |    |

| External trigger using READ pin                                |    |

| Global Shutter external trigger                                |    |

| Rolling Shutter external trigger                               |    |

| Timing diagrams                                                |    |

| Packaging information                                          |    |

| Standard Package drawings                                      |    |

| Scientific Package drawings                                    |    |

| Pin list for both Scientific and Standard packages             |    |

| Monochromatic Quantum Efficiency                               |    |

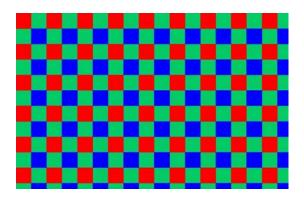

| Color Filter Array (CFA) Option                                |    |

| Cosmetic Specifications                                        |    |

| Storage Conditions                                             |    |

| Handling Precautions                                           |    |

| Soldering Instructions                                         |    |

| Window Cleaning Instructions                                   |    |

| Sensor Package Cleaning Instructions                           |    |

| Revision HistoryDisclaimer                                     |    |

| Contact Information                                            |    |

| Cuitage iiiiuiiialiuii                                         | სა |

# **List of Figures**

| Figure 1. JTAG Interface I/O Timing                                                           | 10 |

|-----------------------------------------------------------------------------------------------|----|

| Figure 2. Functional Control Inputs Timing                                                    | 11 |

| Figure 3. Data and Status Output Timing                                                       |    |

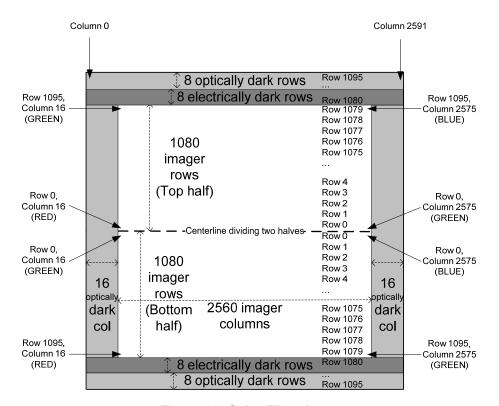

| Figure 4. Floor Plan of the CIS2521 Image Sensor                                              | 13 |

| Figure 5. CIS2521 sensor floor plan with row numbering                                        | 14 |

| Figure 6. Architecture of each half of the CIS2521                                            | 15 |

| Figure 7. 5T pixel schematic                                                                  |    |

| Figure 8. Column readout circuitry                                                            |    |

| Figure 9. Programmable Regions of Interest                                                    | 20 |

| Figure 10. CDS Operation in Rolling Shutter Mode                                              | 22 |

| Figure 11. Integration during Rolling Shutter Mode                                            |    |

| Figure 12. Pseudo single port readout timing                                                  |    |

| Figure 13. Correlated quadruple sampling operation                                            |    |

| Figure 14. Basic Rolling Shutter Mode                                                         |    |

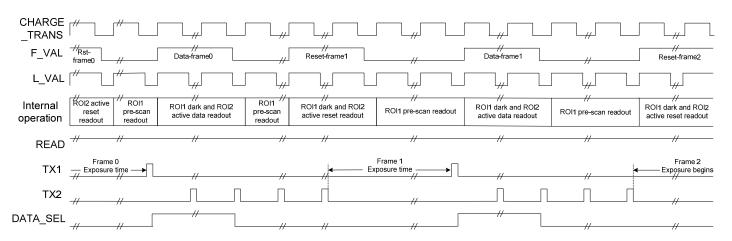

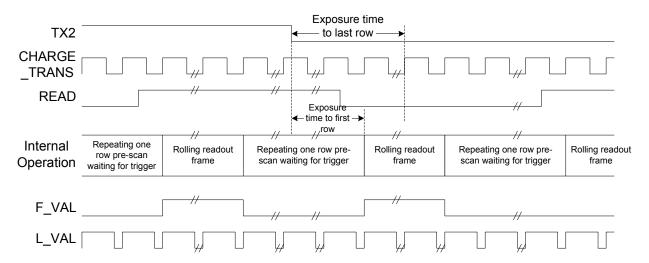

| Figure 15. Rolling Shutter Mode using READ pin to extend exposure time, Reg 2 bit 21 = 0      | 27 |

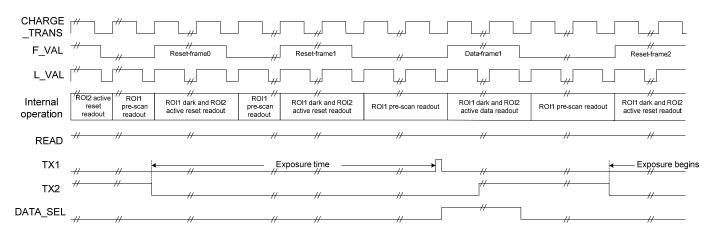

| Figure 16. Basic Global Shutter Mode                                                          | 28 |

| Figure 17. Basic Global Shutter Mode, Short Exposure (Similar to Fig 16 but with more details |    |

| Figure 18. Basic Global Shutter Mode, Long Exposure (Similar to Fig 16 but with more details  |    |

| Figure 19. Global Shutter Mode using READ pin to extend exposure time                         |    |

| Figure 20. Rolling Shutter Mode with External Trigger, Reg 2 bit19=0 and bit23=1              |    |

| Figure 21. Rolling Shutter Mode with External Trigger, Reg 2 bit 19=1 and bit 23=1            |    |

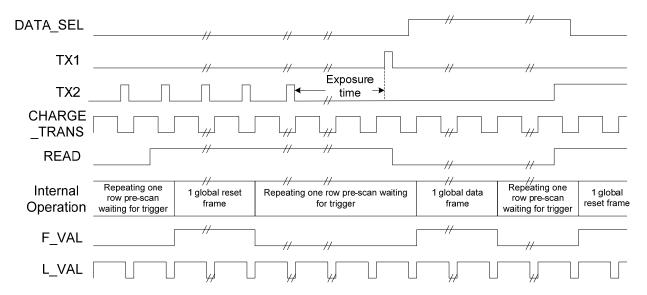

| Figure 22. Global Shutter Mode with External Trigger                                          |    |

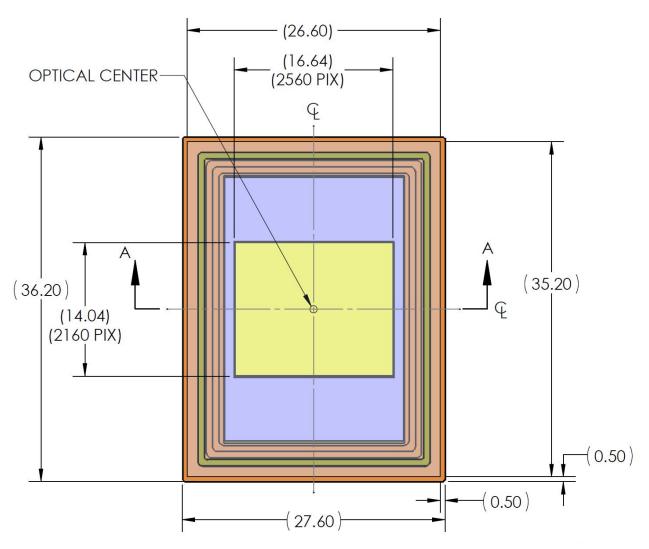

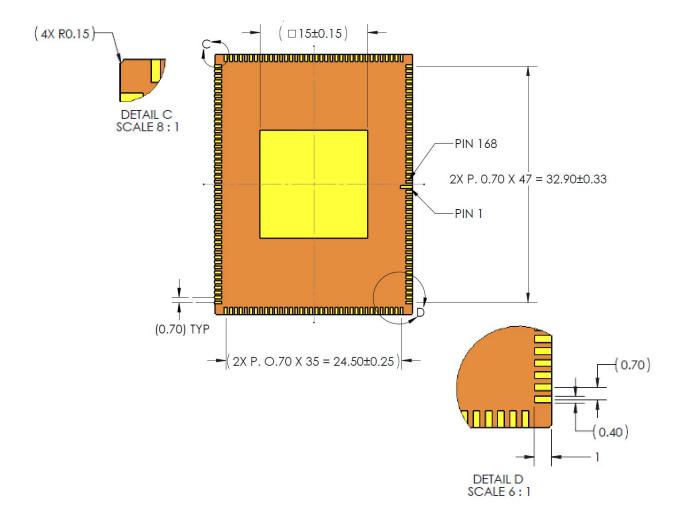

| Figure 23. Top View of CIS2521 Standard Package                                               |    |

| Figure 24. Side View of CIS2521 Standard Package                                              |    |

| Figure 25. Bottom View of CIS2521 Standard Package                                            |    |

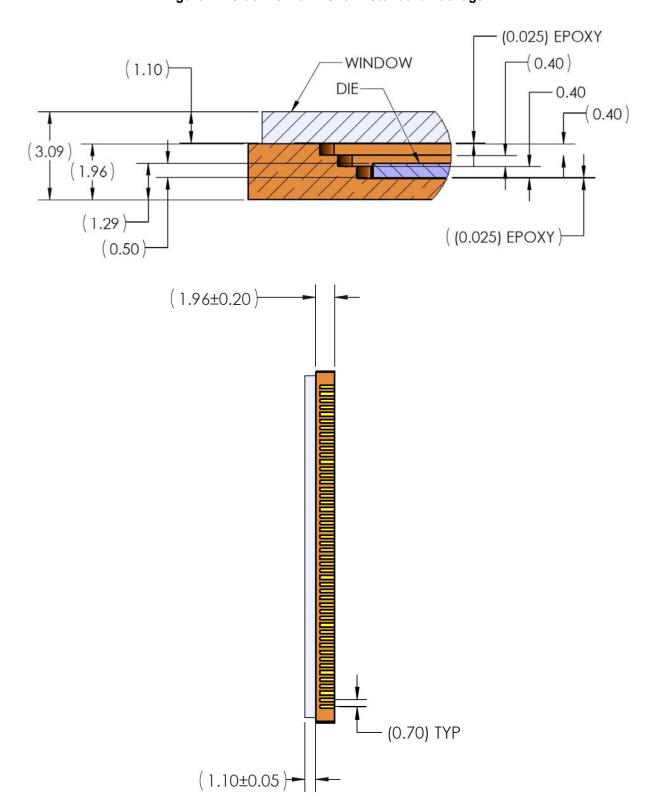

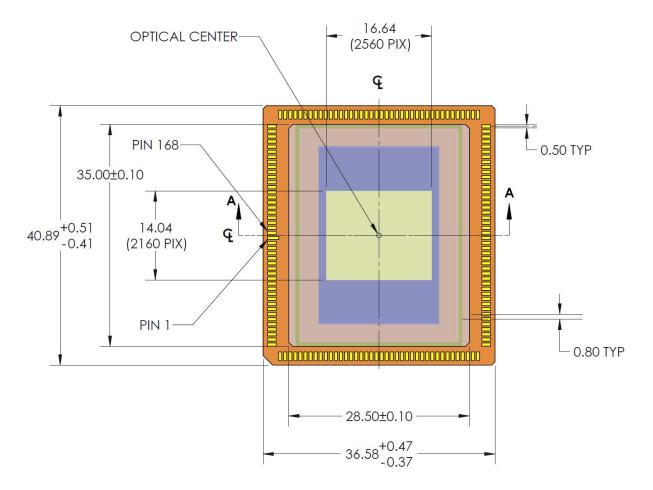

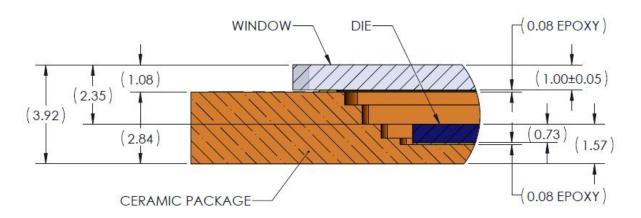

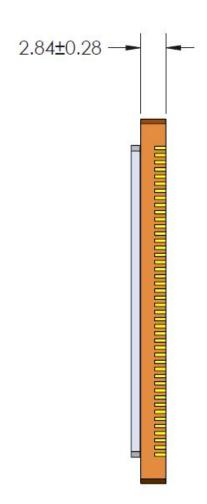

| Figure 26. Top View for CIS2521 Scientific Package                                            |    |

| Figure 27. Side View of CIS2521 Scientific Package                                            |    |

| Figure 28. Bottom View of CIS2521 Scientific Package                                          |    |

| Figure 29. QE versus wavelength curve for monochromatic sensor                                |    |

| Figure 30. Color Filter Array                                                                 |    |

| Figure 31. CFA QE Curves                                                                      | 59 |

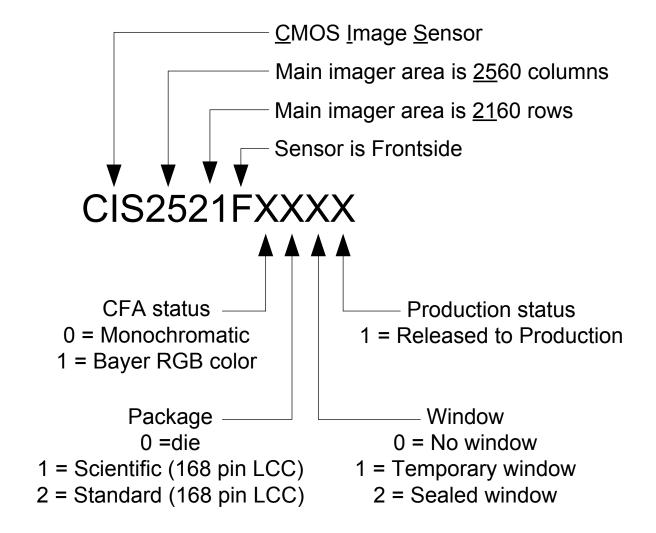

# **Sensor naming convention**

This datasheet will describe the monochromatic and color options for the Scientific and Standard packages. Drawings will assume that the Sealed window option is always used. So, effectively this datasheet covers the four parts CIS2521F0121, CIS2521F1121, CIS2521F0221, and CIS2521F1221.

At the time of this datasheet revision (February 2013), the Backside CIS2521 is not in production. Therefore this datasheet will sometimes use "CIS2521" and "CIS2521F" interchangeably.

## **General Specifications**

| Parameter                          | Typical value                                                                                                                                                     |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Active array size                  | 2560 (H) x 2160 (V), imaging pixels only 2592 (H) x 2192 (V), imaging and dark pixels                                                                             |

| Pixel size                         | 6.5 μm x 6.5 μm                                                                                                                                                   |

| Dimensions of active area (Note 1) | 16639.6 μm (H) x 14039.6 μm (V), imaging pixels only<br>16847.6 μm (H) x 14247.6 μm (V), imaging and dark pixels                                                  |

| Dimensions of die (Note 2)         | 18842 μm (H) x 27642 μm (V), die circuit only<br>18882 μm (H) x 27682 μm (V), including seal ring<br>19002 μm (H) x 28122 μm (V), including saw street (estimate) |

| Shutter type                       | Rolling Shutter, Global Shutter (snapshot). ROI readout capabilities for both shutter types.                                                                      |

| Maximum frame rate (Note 3)        | 100 fps (Rolling Shutter)<br>50 fps (Global Shutter)                                                                                                              |

| Number of readout ports            | 2 (1 for top half array, 1 for bottom half array)                                                                                                                 |

| Maximum line rate (Note 3)         | 109.6 kHz (9.124 μs/line)                                                                                                                                         |

| Maximum pixel rate (Note 3)        | 284 MHz (3.48 ns/pixel)                                                                                                                                           |

| ADC resolution                     | 2 x 11-bit                                                                                                                                                        |

| Column level amplifier gain        | 1x or 2x (low gain output)<br>10x or 30x (high gain output)                                                                                                       |

| Power consumption                  | < 2 W                                                                                                                                                             |

| I/O interface                      | 1.8V LVCMOS and 1.8V HSTL (class I)                                                                                                                               |

| Package type                       | 168-pin LCC                                                                                                                                                       |

**Note 1:** Dimensions are from the lithographic pattern.

**Note 2:** The dimensions for the die circuit area and the seal ring around it are defined by lithography and are accurate to sub-micron tolerances. When the die is cut from the wafer, there may be greater variations depending on the wafer cut process.

**Note 3**: The values for line rate and pixel rate are calculated values based on the assumption of 100 fps operation. If the sensor is running 100 fps, one frame takes 0.01 seconds and there are 1096 lines in a frame (for each sensor half, assuming the default frame size). Therefore each sensor half has a maximum line rate of 109.6 kHz. Each line has 2592 pixels, so the maximum pixel rate is (2592 pixels/line)\*(1096 lines/frame)\*(100 frames/sec) = 284,083,200 pixels/second, or 284 MHz.

Because these values for maximum pixel and line rates are calculated values, what the actually showing is maximum average line rate and maximum average pixel rate. On chip, the maximum SCLK input is 287 MHz, and the digital numbers for each pixel value come out one per SCLK (for each imager half). So actual pixel data may be appearing on the DOUT and DOUT\_LG pins at

the SCLK rate of 287 MHz, at least for the portion of each line time that pixel readout is occurring (2592 SCLKs out of every 2624 SCLKs).

If the 100 fps number is not assumed but is instead calculated from on-chip functionality, a slightly different fps number can be found. In the CIS2521 sensor, the number of clocks per row of pixels is set by JTAG Registers 16 through 47, which together are called the "wavetable". According to both default and recommended wavetable settings, there are 2624 clocks per line. This then correlates to a line time of (2624 clocks/line)/(287 million clocks/sec) =  $9.142 \mu s/line$ . The maximum frame rate then depends on the number of lines in the frame. The number of lines in the frame are controlled by the user loading values into JTAG Registers 6, 7, and 8. With the default values that are automatically loaded at device start up, the frame is 1080 imager lines plus 16 dark lines = 1096 lines. So the Rolling Shutter maximum frame rate with default settings is:

(287 million clocks/sec) / (2624 clocks/line)\*(1096 lines/frame) = 99.79 frames/second

which we round up to 100 fps in the above table. (Obviously much higher frame rates are possible if smaller frame sizes are used in place of the default 1096 lines.) Note that the actual image with the default settings will actually be 1096\*2 = 2192 rows high, since the "1080" and "16" numbers are with respect to the imager half, and the final image consists of both halves.

The maximum frame rate for Global Shutter is always ½ the number for Rolling Shutter, since two frames of sensor readout (the Reset and Data frame) are necessary to construct the final Global Shutter image.

# **Electrical-optical specifications**

| Parameter                   | Specification                                                                                                    | Notes                                                                                             |

|-----------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Intra-frame dynamic range   | 15000:1                                                                                                          |                                                                                                   |

| PRNU                        | < 3% RMS                                                                                                         | at 75% of max output                                                                              |

| Dark current                | < 35 e-/pixel/sec                                                                                                | at 20°C                                                                                           |

| Dark current non-uniformity | < 65 e-/pixel/sec RMS                                                                                            | at 20°C                                                                                           |

| Fixed pattern noise (FPN)   | < 2% RMS                                                                                                         | of the max output                                                                                 |

| Conversion gain (DN/e-)     | High gain output (nominal):  - 1.7 at 30x  - 0.57 at 10x  Low gain output (nominal):  - 0.12 at 2x  - 0.06 at 1x | ADC input range is programmable from 0.4V to 1.55V. So, conversion gain in DN/e- is programmable. |

| Full well capacity (FWC)    | ≥ 30,000 e-                                                                                                      |                                                                                                   |

| Lag                         | < 0.1%                                                                                                           | of maximum output                                                                                 |

| Non-linearity               | < 2%                                                                                                             |                                                                                                   |

| Fill factor with microlens  | > 0.9                                                                                                            |                                                                                                   |

| Microlens F#                | 1.5 for monochromatic sensor 1.6 for color sensor                                                                |                                                                                                   |

| Peak QE                     | ≥ 0.55                                                                                                           | at 600nm                                                                                          |

| MTF                         | ≥ 0.4                                                                                                            | at 600nm                                                                                          |

| Temporal read noise         | < 2 e- RMS @ 30 fps Rolling<br>Shutter readout                                                                   | Median value of read noise distribution from high gain output (30x gain)                          |

| Spectral sensitivity range  | 400 – 700nm                                                                                                      | See QE plots (Figure 29 and Figure 31) for spectral sensitivity in the Near IR out to 1100 nm     |

The above specifications are from CIS2521F devices running in Rolling Shutter mode. Although the CIS2521F runs in Global Shutter mode, BAE does not guarantee any performance specifications for Global Shutter mode. However, the functionality of all sensors to operate in Global Shutter mode is verified at wafer test.

For sensor performance specifications in photometric units, contact Technical Support at <a href="mailto:cams.techsupport@baesystems.com">cams.techsupport@baesystems.com</a>.

# **Recommended Operating Conditions**

| Parameter                                                                                                                         | Definition                                                                                                                                               | Min   | Nom                                       | Max   | Units |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------|-------|-------|

| AVDD                                                                                                                              | Analog circuits power supply (avg 250 mA, Peak at 355 mA on 5% duty cycle) Note 1                                                                        | 3.135 | 3.3                                       | 3.465 | V     |

| AVDD_PIX                                                                                                                          | Pixel source follower power supply (25 mA nom)                                                                                                           | 3.135 | 3.3                                       | 3.465 | V     |

| AVDD_RST1                                                                                                                         | Pixel reset power supply1 (1 mA)                                                                                                                         | 2.2   | 3.00                                      | 3.3   | V     |

| AVDD_RST2                                                                                                                         | Pixel reset power supply2 (1 mA)                                                                                                                         | 2.2   | 3.00 (RS)<br>or 2.739<br>(GS)<br>(Note 2) | 3.3   | V     |

| DVDD_3V3                                                                                                                          | Row circuits and level shifters power supply (1mA)                                                                                                       | 3.135 | 3.3                                       | 3.465 | V     |

| DVDD                                                                                                                              | Digital circuits power supply (290 mA @287MHz)                                                                                                           | 1.71  | 1.8                                       | 1.89  | V     |

| DVDD_IO                                                                                                                           | I/O circuits power supply (270 mA @287MHz) Note 3.                                                                                                       | 1.71  | 1.8                                       | 1.89  | V     |

| VTX1_POS                                                                                                                          | TX1 Transfer gate positive power supply (1mA in Rolling Shutter, 200 mA for 1µsec/pulse during Global Shutter)                                           | 2.90  | 3.3                                       | 3.60  | V     |

| VTX2_POS  TX2 Transfer gate positive power supply (1mA in Rolling Shutter, 200 mA for 1µsec/pulse during Global Shutter) (Note 4) |                                                                                                                                                          | 2.90  | 3.3                                       | 3.60  | V     |

| VTX1_NEG                                                                                                                          | TX1 Transfer gate negative power supply (same current max as VTX1_POS)                                                                                   | -1.5  | -0.4                                      | +0.3  | V     |

| VTX2_NEG                                                                                                                          | TX2 Transfer gate negative power supply (same current max as VTX2_POS)                                                                                   | -1.5  | -0.4 or<br>+0.8<br>(Note 5)               | +0.85 | V     |

| T <sub>operation</sub>                                                                                                            | Sensor junction temperature                                                                                                                              | -40   | 30                                        | +55   | °C    |

| RTRIM                                                                                                                             | Bias resistor for bandgap based internal bias generator (current through resistor is approximately 100µA; for low noise, place resistor close to sensor) | 11K   | 12.28K<br>(Note 6)                        | 13.5K | Ω     |

| PTAT R <sub>OUT</sub>                                                                                                             | Output resistance of PTAT temperature sensor                                                                                                             |       | 100K<br>(Note 7)                          |       | Ω     |

**Note 1:** The relevant period for this duty cycle is the row readout time, which is 2624 SCLKs for both the default and recommended wavetables. The 5% number comes from the percentage of clock cycles that buff\_en (wavetable bit 8) is high during the 2624 SCLK row readout time.

**Note 2:** The recommended voltage for AVDD\_RST2 is 3.00 Volts when running in Rolling Shutter and 2.739 Volts when running in Global Shutter. If the user plans on switching between Rolling and Global Shutter, the power to AVDD\_RST1 must be switchable between these two

voltages. For Global Shutter operation, it is critical for there to be a tightly controlled differential between AVDD\_RST1 and AVDD\_RST2 – a 261 mV differential in the case of AVDD\_RST1 = 3.000 V and AVDD\_RST2 = 2.739 V. This is particularly critical for high gain Global Shutter operations. This differential voltage controls the DN level of the Reset frame, with a target of about 300 DN for the Reset frame being the goal. At 10x gain, each 10 mV of differential voltage changes the Reset level by 100 DN. At 30x gain, each 10 mV of differential voltage changes the Reset level by 300 DN.

**Note 3:** Normally the DOUT and DOUT\_LG pins send their outputs to another chip (typically an FPGA) to be decoded from Gray code to binary. If the traces connecting the imager to this external chip are too long, the user may wish to add termination at the inputs to this other chip to prevent signal reflection. Adding such termination will increase the current requirement on DVDD\_IO. (In practice, no BAE-designed cameras have required such termination.)

Note 4: In Rolling Shutter, the TX2 gate is not typically pulsed and the TX1 gate only gets pulsed for one row of pixels at a time. The current requirements of VTX1\_POS, VTX2\_POS, VTX1\_NEG, and VTX2\_NEG are therefore minimal (< 1 mA) in typical Rolling Shutter applications. In Global Shutter, both the TX1 and TX2 gates pulse globally (i.e. every pixel in the sensor pulsing simultaneously). In Global Shutter therefore, VTX1\_POS, VTX2\_POS, VTX1\_NEG, and VTX2\_NEG all must have enough current capacity to source or sink the necessary currents. For a Global TX2 pulse, the VTX2\_POS must supply 200 mA on the rising edge of that pulse and the VTX2\_NEG must sink 200 mA on the falling edge of that pulse. Similarly, for a Global TX1 pulse, the VTX1\_POS must supply 200 mA on the rising edge of that pulse and the VTX1\_NEG must sink 200 mA on the falling edge of that pulse. At a minimum, Global Shutter operation typically requires a single Global TX2 pulse and a single Global TX1 pulse. But sometimes (see Figures 17 and 22) there are Global TX2 pulse trains where these 200 mA source/sink current requirements are needed each line time. The 200 mA number is for the imager as a whole. The number for each imager half is 100 mA.

**Note 5:** The recommended voltage for VTX2\_NEG is -0.4 Volts when running in Global Shutter. -0.4 Volts is also recommended when running in Rolling Shutter under low light conditions. But when running in Rolling Shutter under high light conditions, +0.8 Volts is recommended. This voltage setting will make use of the TX2 gate's anti-blooming functionality

**Note 6:** There are two RTRIM pins on the packaged part, pins 75 and 96. For each pin, a 12.28  $K\Omega$  resistor should be attached with one end to the RTRIM pin and with the other end at analog ground. These two resistors are important in order to power the column amplifier circuits and insure functioning DOUT and DOUT LG outputs.

**Note 7:** The  $100 K\Omega$  resistance is an internal resistance inside the chip. The user does not need to add any external resistor. The  $100 K\Omega$  number is given so that when the user measures the PTAT voltage, the user will choose a voltmeter with an internal impedance much greater than  $100 K\Omega$  so as not to load the PTAT pin and get an inaccurate voltage reading. PTAT stands for Proportional To Absolute Temperature.

# **Timing Specifications**

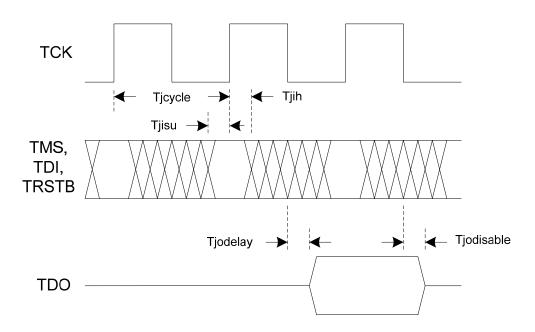

## **JTAG Interface**

Figure 1. JTAG Interface I/O Timing

| Parameter  | Definition                                                       | Unit | Min | Max | Note |

|------------|------------------------------------------------------------------|------|-----|-----|------|

| Tjcycle    | TCK clock cycle time                                             | ns.  | 40  |     |      |

| Tjdc       | TCK clock duty cycle                                             | %    | 45  | 55  |      |

| Tjisu      | JTAG input setup time for TMS, TDI, and TRSTB                    | ns.  | 2.0 |     |      |

| Tjih       | JTAG input hold time for TMS, TDI, and TRSTB                     | ns.  | 1.0 |     |      |

| Tjodelay   | JTAG output delay time for TDO signal from falling edge of TCK   | ns.  |     | 8.0 |      |

| Tjodisable | JTAG output disable time for TDI signal from falling edge of TCK | ns   |     | 6.0 |      |

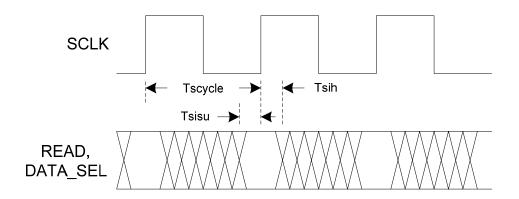

# **Functional Control Inputs**

**Figure 2. Functional Control Inputs Timing**

| Parameter | Definition                      | Unit | Min  | Max | Note |

|-----------|---------------------------------|------|------|-----|------|

| Tscycle   | SCLK clock cycle time           | ns.  | 3.48 |     |      |

| Tsdc      | SCLK clock duty cycle           | %    | 48   | 52  |      |

| Tsjitter  | SCLK peak to peak cycle jitter  | ps.  |      | 150 |      |

| Tsisu     | READ, DATA_SEL input setup time | ns.  |      | 1.0 |      |

| Tsih      | READ, DATA_SEL input hold time  | ns.  |      | 0.5 |      |

# **Data and Status Outputs**

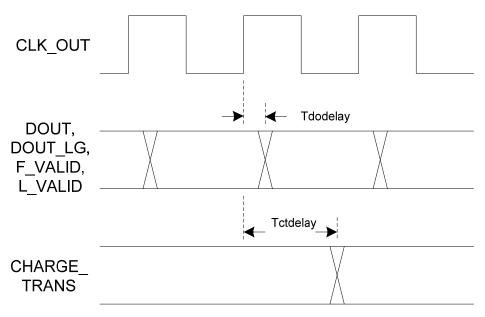

Figure 3. Data and Status Output Timing

| Parameter | Definition                                        | Unit | Min | Max | Note                  |

|-----------|---------------------------------------------------|------|-----|-----|-----------------------|

| Tdodelay  | DOUT, DOUT_LG, F_VALID, L_VALID output delay time | ns   |     | 1.0 | Source<br>Synchronous |

| Tctdelay  | CHARGE_TRANS output delay time                    | ns   |     | 2.5 |                       |

## **Device Architecture**

## Sensor Floor plan

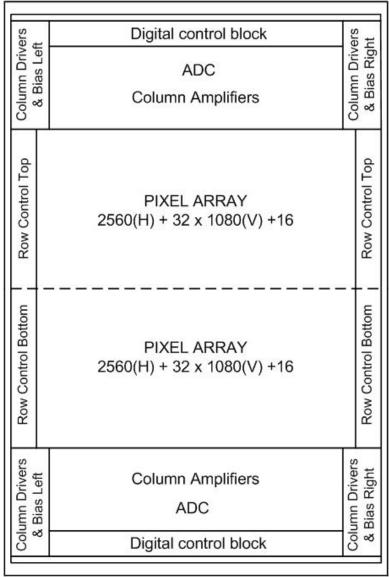

Figure 4. Floor Plan of the CIS2521 Image Sensor

The CIS2521 floor plan is shown in Figure 4. The sensor consists of two independent halves. The pixel orientation is identical in both halves. The column amplifier circuits, ADCs and the digital control block (DCB) are located at the top and bottom of the array. The row control circuits are located on both sides of the pixel array.

The 2560 by 2160 active imager pixel array is surrounded on all sides by a 16 pixel wide dark region. Rows are numbered with row 0 in the center and with numbers increasing moving outward from the center. Because the two imager halves are to be treated independently, the top and bottom halves use the same row numbering scheme without contradiction.

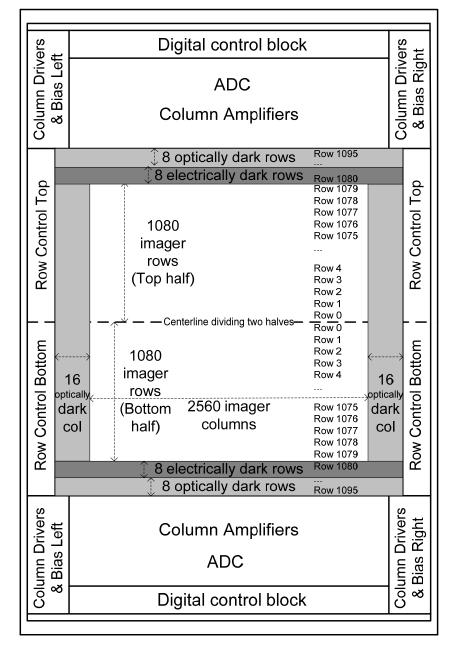

Figure 5. CIS2521 sensor floor plan with row numbering

The optically dark rows are covered with metal so light cannot enter. The electrically dark rows are also covered with metal so light cannot enter; but in addition, all the pixels of these rows have the gates of their TX2 transistors permanently tied to AVDD. This makes them "electrically dark" as well as "optically dark", because any charge in these dark rows (from dark current, for example) is removed via the TX2 charge dump, which is permanently active for these rows.

#### **Sensor Architecture**

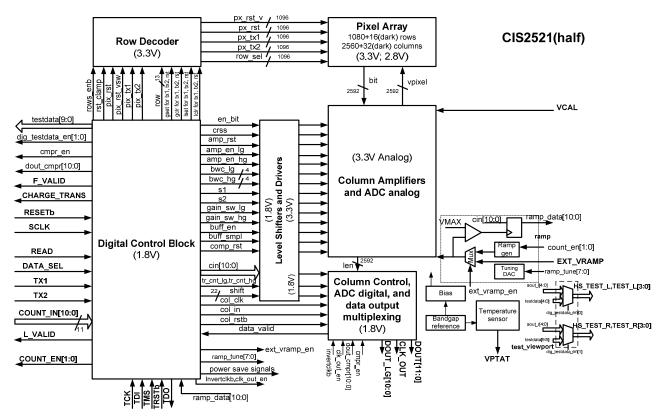

Figure 6. Architecture of each half of the CIS2521

Figure 6 illustrates the architecture of each half of the sensor. The DCB includes all of the digital circuits required for programming and controlling the device. The DCB contains five major subsections: the JTAG tap controller, the JTAG registers, the Gray code ramp counter, the row controller, and the waveform generator.

The row decoder consists of a 13-bit decoder and 1096 row-driver circuits that control each row of pixels. There are five output signals for each pixel row: PX\_TX1, PX\_TX2, PX\_RST, PX\_RST\_V, and ROW\_SEL.

Column control signals are generated in the DCB and routed to the "Level Shifters and Drivers" on both sides of the column circuitry. The "Level Shifter and Drivers" convert incoming 1.8V LVCMOS signals into 3.3V LVCMOS signals for controlling the column level amplifiers and ADCs. This block also contains the bias generator circuitry. There are two bias references that can be selected via JTAG Register 9, bit 25. The first bias reference, based on the internal bandgap reference voltage, allows the bias point to be changed via an external resistor RTRIM. It achieves the minimum bias variation as a function of temperature (Register 9, bit 25 = 0, the default). The second bias reference, based on an internal resistor, achieves the lowest readout noise (Register 9, bit 25 = 1). Even if the internal resistor is used by setting Register 9 bit 25 to 1, external RTRIM resistors at pins 75 and 96 should still be added.

Separate power supplies are used for the pixel core, analog amplifiers and ADCs, the pad ring, and the digital circuitry. A voltage ramp generator is integrated on the sensor to drive the single

slope ADCs in each column. The offset and swing of the ramp generator can be programmed via the JTAG interface.

The user must provide a system clock which synchronizes all the operations in the chip. The row and column control clocks, and the built-in Gray code counter for the single slope ADCs are all derived from the system clock.

The user has the ability to change the timing of the internal control signals by reprogramming the JTAG registers.

An on-chip PTAT temperature sensor provides a continuous analog output voltage for monitoring the die temperature.

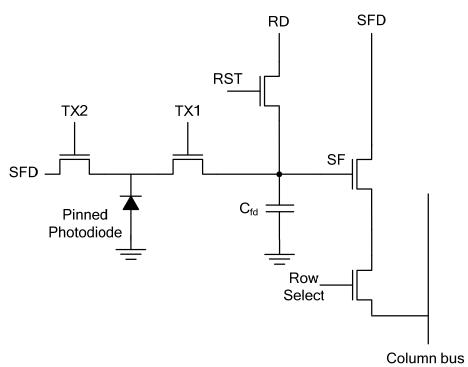

#### Pixel architecture

Figure 7. 5T pixel schematic

A schematic diagram of the 5T pinned photodiode pixel is shown in Figure 7. The pinned photodiode inside of each pixel starts to integrate charge as soon as the transfer gate TX1 is turned off. Then when the transfer gate TX1 is turned on, the integrated charge in the photodiode is dumped onto the floating diffusion node and read out as a voltage signal by the source follower. The TX2 gate serves both as a global reset gate and a lateral anti-blooming protection gate.

## Column readout circuitry

Figure 8. Column readout circuitry Programmable **Dual Single** Low Noise Slope 11 bit Dual Column ADC Level Amplifers Column Analog Bus Low gain Digital Memory 1x, 2x 22 Bit Output Analog Memory High Digital gain Memory 10x, 30x Common Programmable Ramp Signal Common Gray Code Counter Input

Figure 8 shows the amplifier and ADC structure used in each column of the sensor. This architecture was selected to minimize the sensor read noise while maximizing dynamic range.

There are two amplifiers per column simultaneously generating low gain and high gain output signals. The gain of each amplifier is selected to either maximize the full well capacity, i.e. 1x gain, or to minimize the read noise, i.e. 30x gain. The amplifier output gain is further controlled by the settings of the gain\_sw\_lg and gain\_sw\_hg signals (via JTAG Register 2, bits 4 and 5). When gain\_sw\_lg is set to 1, the low gain output is 1x, if gain\_sw\_lg is set to 0, then the low gain output is 2x. On the other hand, when gain\_sw\_hg is set to 1, the high gain output is 10x and when gain\_sw\_hg is set to 0, the high gain output is 30x.

In addition to gain, the bandwidth of the column level amplifiers is also programmable via JTAG Register 2, bits 6 to 13. Each column also contains two 11-bit single slope ADCs. The outputs of the amplifiers and the outputs of the ADCs are double buffered to maximize the line rate of the sensor.

The data output bus is 22 bits wide with DOUT\_LG[10:0] representing the low gain data and DOUT[10:0] representing the high gain data. Because the counter input to the ADC is in Gray code, the DOUT[10:0] and DOUT\_LG[10:0] outputs will be in Gray code. The user will have to convert these outputs from Gray code to binary off-chip.

#### **Sensor Data**

After the analog pixel data is digitized, the 22-bit pixel Gray code output data is sent out through two registers to the output pads. The low gain data are delivered at the 11-bit output port DOUT\_LG[10:0], and simultaneously, the high gain data are presented at the 11-bit output port DOUT[10:0].

A source synchronous output clock CLK\_OUT is provided with the output data. CLK\_OUT is used to register DOUT\_LG[10:0] and DOUT[10:0]. CLK\_OUT can be inverted or disabled via a JTAG register.

## **Sensor Interface**

#### **JTAG Interface**

| Name  | Direction | Description                           |

|-------|-----------|---------------------------------------|

| TCK   | Input     | JTAG clock                            |

| TDI   | Input     | JTAG serial data input                |

| TMS   | Input     | JTAG mode select control              |

| TRSTB | Input     | JTAG state machine reset (active low) |

| TDO   | Output    | JTAG serial data output               |

## **Control Signals**

| Name                    | Direction    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DATA_SEL                | Input        | Selects between a Data (1) or Reset (0) frame readout in Global Shutter mode. Toggling this signal also switches between wavetable A (0) and B (1). JTAG write access to the wavetable is the complement of the table being used for readout. This input is not used for frame selection in Rolling Shutter mode since the distinction between Reset frame and Data frame is not relevant, though it is set to DATA_SEL = 0 in Rolling Shutter because Rolling Shutter uses wavetable A. |  |  |

| READ                    | Input        | READ has multiple functions depending on the sensor's mode of operation. It controls external start/pause of the row counter and readout activities in internally triggered readout modes. It is also used for external triggering in external triggered readout mode. It can also be used to synchronously reset the sensor operation.                                                                                                                                                  |  |  |

| RESETB                  | RESETB Input | Active low reset input (asynchronous). RESETB = 0 resets the sensor and loads the JTAG registers with default values.                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| SCLK                    | Input        | System clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| CHARGE_<br>TRANS Output |              | Marker pulse indicating when data sampling is occurring for the selected row. This signal comes directly from the wavetable without any modification.                                                                                                                                                                                                                                                                                                                                    |  |  |

| F_VALID                 | Output       | Frame valid output, high from beginning of first row to end of last row including dark rows but not pre-scan rows. The timing of rising and falling edge is from the wavetable.                                                                                                                                                                                                                                                                                                          |  |  |

| Name    | Direction | Description                                                                                 |

|---------|-----------|---------------------------------------------------------------------------------------------|

| L_VALID | Output    | Line valid output indicates valid line data. This signal comes directly from the wavetable. |

#### **Global Shutter Readout Mode Pixel Control**

| Name | Direction | Description                                                                                                                                                                                                           |

|------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX1  | Input     | Global Shutter readout mode charge transfer pulse.                                                                                                                                                                    |

| TX2  | Input     | Exposure control / charge dump signal. Although not generally used for Rolling Shutter (see Figures 14, 15, and 20), this signal can have the same exposure control function in Rolling Shutter mode (see Figure 21). |

Please refer to the CIS2521 Programming Manual for additional information.

## Power up sequence

We recommend that the power up sequence follows the order shown below:

- 1. First, DVDD and DVDD\_IO should be powered-up with all the analog supplies held low, with DVDD 3V3 held low, and with both RESETB and READ held low.

- 2. Next, SCLK should be activated (SCLK\_TP and SCLK\_BT if running both halves) for a minimum of 8 cycles before proceeding.

- 3. Then, the sensor should be taken out of reset with both RESETB and READ going high. If both sensor halves are to be frame-synchronized, the READ\_TP and READ\_BT signal edges have to be applied simultaneously. SCLK should be clocked for at least one frame time before proceeding to next step.

- 4. At this point, taking the sensor back into reset is optional. (For example, setting the READ pin to 0 at this point would make it possible to program the registers with non-default values. When this task is done, READ should be set high again.)

- 5. Now, AVDD and all other analog power supplies can be brought up. DVDD\_3V3 is also to be brought up at this time.

## Power down sequence

All the power supplies can be brought down simultaneously.

## Selective component power down

A JTAG register (address 3) is provided to selectively power down individual circuits in order to reduce noise and power dissipation of the sensor under some modes of operation. This register is activated by setting JTAG Register 2 (mode register) bit 25 (low power activation) to 1.

#### **Readout Modes**

## **Region of Interest**

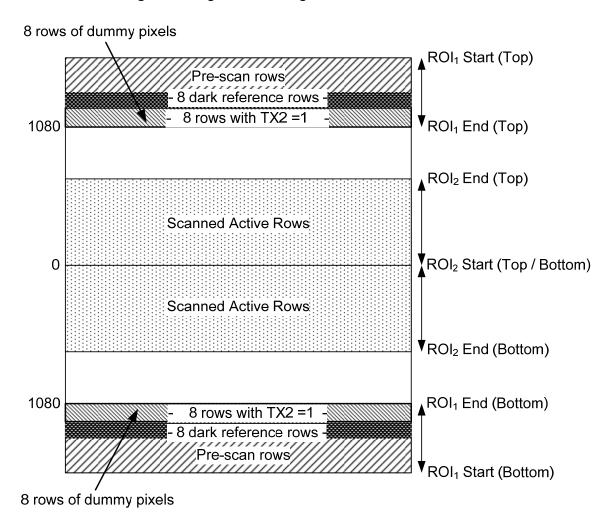

Figure 9. Programmable Regions of Interest

The row control supports two regions of interest (ROI). The first ROI defines the non-imaging region of interest: dark rows and pre-scan rows. It has a programmable size (JTAG Register 8) and a fixed end address of 1080 pointing to the start of the 8 dummy (also called "electrically dark") rows, the pixels of which are optically shielded and have their TX2 gates tied to AVDD to dump all the charge out. The next 8 rows of the first ROI are dark reference rows where the pixels are covered by an opaque metal light shield. A size of 0 will suppress the output from this first ROI region. The direction of counting is always down, i.e. for a ROI<sub>1</sub> size greater than 0, counting will be from (1079 + size) down to 1080. If the row address is greater than 1095, no actual row is selected and the chip output data would correspond to background noise of the column circuits. This operation is termed "pre-scan". For the pre-scan rows, the background noise level of the column amplifier circuits is equal to the floating diffusion node voltages of the last row of ROI2 to be read out. (When the number of pre-scan values is large, it is possible for dark current to build up on the floating diffusion nodes over the pre-scan readout period.) Pre-scan rows are also called virtual rows.

The second ROI is the region that contains all the light sensitive pixels. This region is called the active imager region. It has programmable start and end addresses. The counting direction of this ROI is computed automatically from the starting and ending addresses. If the ending address is greater than the starting address, the counting direction is from the center of the imager outward (i.e. up for the top half of the imager, down for the bottom half). Otherwise it is in the reverse direction (i.e. row counting proceeds toward the direction of the imager center). Figure 9 schematically shows the two ROIs in the top and bottom halves of the sensor.

Normally, a frame of data consists of the ROI1 rows preceding the ROI2 rows (pre-scan/dark/active imager). This order can be reversed if Register 2 bit 22 is set to 1 (not the default). In that case, a frame consists of the ROI2 rows followed by the ROI1 rows (active imager/pre-scan/dark).

L\_VALID is asserted once each row readout, whether that row is pre-scan, dark, or active imager. F\_VALID is asserted high once the first physical row of the frame is read out and goes low only after the last physical row of the frame is read out. Physical rows are dark rows and active imager rows. F\_VALID will be low and stay low during the readout of pre-scan rows.

## **Rolling Shutter readout**

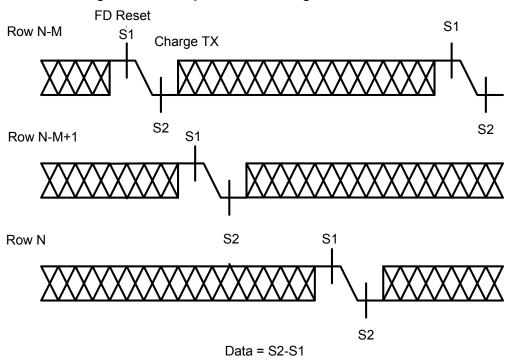

Rolling Shutter is the standard readout method for CMOS image sensors. When READ is asserted in Rolling Shutter mode, one row at a time is sequentially processed until the frame is completely read out. In video readout mode, i.e. when READ is always asserted, frames are continuously read out, separated only by a programmable frame blanking time. Note that the frame blanking time is determined by the number of pre-scan lines in each image. Readout of each row consists of four separate operations. The first operation is resetting the floating diffusion nodes in each pixel. The second operation is reading the reset voltage out via the source follower transistor in each pixel. The third operation is transferring charge from the pinned photodiode to the floating diffusion node, via TX1, and the last operation is reading out the signal voltage. At the edge of the array, column parallel circuitry amplifies, subtracts, and digitizes the row data. The difference between the reset voltage the signal voltage is a form of correlated double sampling (CDS). CDS removes kTC, i.e. reset, noise on the floating diffusion node, and suppresses the source follower 1/f noise. This readout mode achieves the lowest read noise available for the CIS2521.

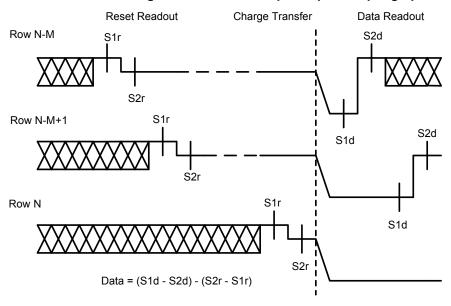

The CDS operation in Rolling Shutter mode is illustrated in Figure 10. The floating diffusion voltages of rows N-M, N-M+1, and N are shown. The reset sample for each row is S1 and the data sample for each row is S2. The final pixel value is the difference between S2 and S1.

Figure 10. CDS Operation in Rolling Shutter Mode

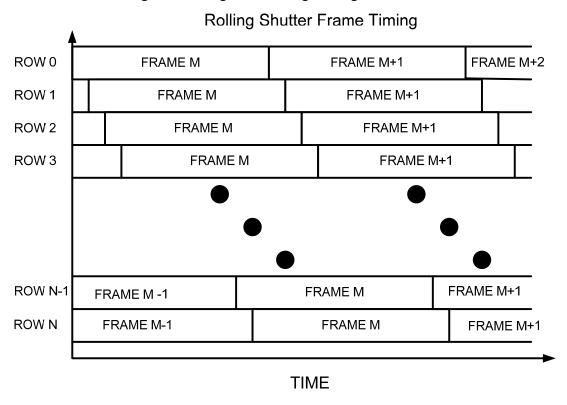

In Rolling Shutter readout, each row in the sensor integrates photo-charge for the same amount of time but the exact time interval is different. Moreover, the integration interval for row N+1 is shifted by one line time in comparison to row N. Figure 11 illustrates this effect.

Figure 11. Integration during Rolling Shutter Mode

### Seamless change of integration time in Rolling Shutter readout

Seamless change of integration time in Rolling Shutter readout mode is implemented on this sensor to allow standard auto exposure algorithms to be implemented in a camera. This operation is always active in Rolling Shutter readout mode. Seamless change of integration time is implemented in the sensor by forcing the integration time of each row in each frame to be the same. This enables smooth video output when integration time is used as an electronic shutter.

#### Pseudo single port readout mode

By programming the starting ROI address, the ending ROI address, enabling dark row operation and reset using the READ pin function, both halves of the sensor can be operated in tandem synchronously, behaving as if the sensor had only one output port. Data will be outputted from one output port while the other output port is generating pre-scan and dark row data as illustrated in the following diagram. Note that time is increasing from left to right in the diagram. The shaded regions are where F\_VALID is asserted.

dark dark dark pre-scan pre-scan First Half pre-scan data A data A data A Second Half data B pre-scan B data B pre-scan B data B pre-scan B

Figure 12. Pseudo single port readout timing

As illustrated in Figure 12, it is a requirement that the pre-scan and dark region of one half of the sensor must match the data region of the other half of the sensor for seamless synchronous operation. It is also required that one half of the sensor has Register 2 bit 22 equal to 0 (the

default) so the readout order for the frame is pre-scan rows / dark rows / active imager rows ("data") while the other half of the sensor has Register 2 bit 22 equal to 1 so the readout order for the frame is active imager rows ("data") / pre-scan rows / dark rows.

#### **Global Shutter**

Global Shutter operation allows every pixel in the sensor to integrate charge during the same time period. This minimizes motion artifacts when compared with Rolling Shutter operation. The CIS2521 performs Global Shutter using TX1 (transfer charge from pinned photodiode to floating diffusion) and TX2 (dump charge from pinned photodiode) to simultaneously control the end and start of integration respectively. Both TX1 and TX2 are active high, i.e. they transfer or dump charge when high.

In order to achieve low noise readout, correlated double sampling (CDS) must be performed to mitigate the effects of reset and 1/f noise in each pixel. Due to the global operation of TX1, the typical Rolling Shutter-type readout method (scrolling reset and then readout of each line) cannot be used to perform CDS. Therefore correlated quadruple sampling (CQS) is used to minimize read noise. CQS requires that the sensor be read out twice to construct each image frame. Moreover, a Reset frame and a Data frame are required for each image and the final image is created by subtracting the Reset frame from the Data frame. The first readout, i.e. the Reset frame, is a measurement of the kTC noise charge on the floating diffusion in each pixel. The second readout, i.e. the Data frame, is a measurement of the charge transferred from the pinned photodiode onto the floating diffusion.

Figure 13 illustrates the operation of CQS. S1r and S2r are reset samples collected during a Reset frame, and S1d and S2d are data samples collected during a Data frame. During a Reset frame each row within the ROI is read out sequentially. When a given row is selected all of the floating diffusion capacitances in that row are first hard reset to RD via the reset transistor in each pixel. Then, while the reset transistor is on, S1r samples the pixel voltage. Then the reset gate is turned off and S2r samples the floating diffusion, i.e. the noise charge. After all of the rows in the Reset frame are read out, charge can be transferred from the pinned photodiode to the floating diffusion capacitance in each pixel. After charge is transferred to the floating diffusion capacitance a Data frame can be collected. Similar to the readout of a Reset frame, a Data frame is read out sequentially row by row. While a given row is selected, all of the floating diffusion capacitances in that row are first sampled via S1d. Then the reset transistor in each pixel is turned on and S2d samples the pixel voltage. Finally the Reset frame is subtracted from the Data frame, external to the sensor, forming the image S1d-S2r. Note that this assumes that S1r and S2d are the same value, which is only true if RD is noiseless. Therefore, the noise voltage on RD is critical to the final read noise of the sensor in Global Shutter operation.

Figure 13. Correlated quadruple sampling operation

The following sections discuss Global Shutter operation in more detail and explain Reset frame and Data frame readout.

#### Reset frame readout

In Global Shutter mode, reset readout occurs when the DATA\_SEL is low and the READ is high. Each Reset frame begins at the first row of ROI $_1$  and ends with the last row of ROI $_2$ . For example, if ROI $_1$  start = 2047 and ROI $_1$  stop = 1080 then 952 pre-scan lines and 16 optically dark lines are sequentially read out from ROI $_1$ . If ROI $_2$  start = 11 and ROI $_2$  stop = 1070 then the row counter counts up and 1060 active rows are read out of the sensor in ROI $_2$ . Note that after row 1080 is read out of ROI $_1$  then the next row, i.e. the first row of ROI $_2$ , is row 11. If DATA\_SEL is held low and READ is held high, Reset frames will continue to be generated by the sensor and the row counter will continuously cycle through the row values in the current ROIs.

In video mode every Reset frame needs to be followed by a Data frame. Note that just like Rolling Shutter mode, the frame blanking time is determined by the number of pre-scan lines in each image. When switching between a Reset frame and a Data frame, DATA\_SEL should be toggled during the frame blanking period.

#### Data frame readout

In Global Shutter mode, data readout occurs when the DATA\_SEL is high and the READ is high. Each Data frame begins at the first row of ROI<sub>1</sub> and ends with the last row of ROI<sub>2</sub>. For example, if ROI<sub>1</sub> start = 2047 and ROI<sub>1</sub> stop = 1080 then 952 pre-scan lines and 16 optically dark lines are sequentially read out from ROI<sub>1</sub>. If ROI<sub>2</sub> start = 11 and ROI<sub>2</sub> stop = 1070 then the row counter counts up and 1060 active rows are read out of the sensor in ROI<sub>2</sub>. Note that after row 1080 is read out of ROI<sub>1</sub> then the next row, i.e. the first row of ROI<sub>2</sub>, is row 11. If DATA\_SEL is held high and READ is held high, Data frames will continue to be generated by the sensor and the row counter will continuously cycle through the row values in the current ROIs. To perform correlated quadruple sampling, a Reset frame must be read out before each Data frame. When performing long integrations (greater than one frame time), multiple Reset frames may occur before a Data frame. For correct CQS sampling, the pair of frames chosen for CQS should be the Data frame and the Reset frame that occurs just before it.

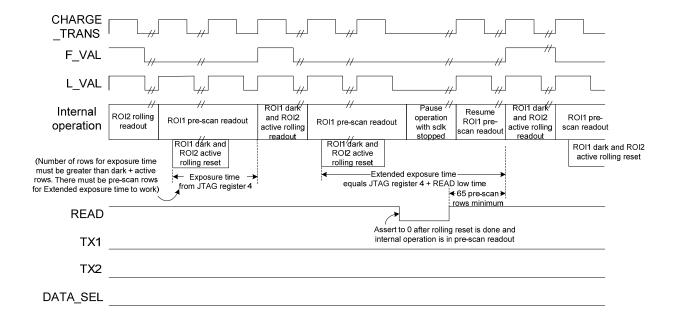

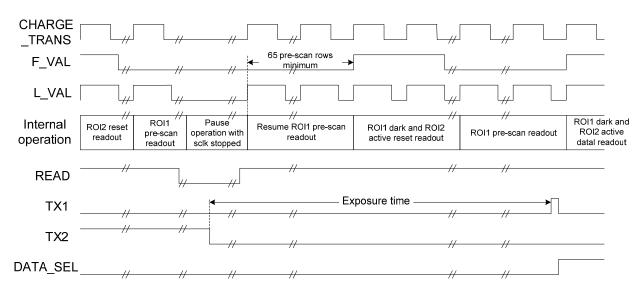

### Pause/Resume using READ pin

The READ pin switching to 0 will glitchlessly stop SCLK when JTAG Register 2 (mode register) bit 21 is 0, resulting in a "zero activity" pause operation. All sensor activities other than JTAG write or reset will be frozen. The assertion of the READ pin to 1 will cause SCLK to resume normal sensor operation. While the clock is stopped, it is possible that the voltage ramp generator will lose synch. The voltage ramp generator will take up to 65 row periods to stabilize.

### Reset using READ pin

When JTAG Register 2 (mode register) bit 21 is 1, READ resets the sensor state (except the JTAG register values will not be forced back to their default values). This behavior is necessary to either:

- a. start operation from a controlled start point, or

- b. start synchronously for pseudo single port readout operation.

## External trigger using READ pin

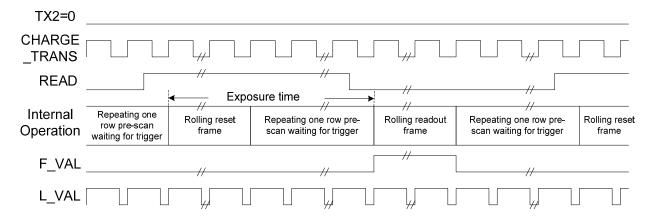

When JTAG Register 2, bit 23, is 1, it overrides the setting of bit 21 as described above and modifies the behavior of the READ pin. This is called external trigger mode. In this mode, the READ pin is sampled using the falling edge of CHARGE\_TRANS. A change in the value of READ before and after the sample qualifies as a transition on READ.

#### Global Shutter external trigger

In this mode, each transition of the READ pin causes one and only one frame of either reset or data operation (depending on the value of DATA\_SEL) before the sensor goes into an "idling" state where only one virtual row is continuously being accessed. In the "idling" state, the sensor is waiting for the next transition on READ. While the sensor is "idling", external control signals TX1 and TX2 can be applied to precisely control the start and duration of the frame exposure. The response time of the sensor to a READ transition is one row time, i.e. the amount of time required to switch from the virtual row to a valid row.

#### Rolling Shutter external trigger

In this mode, each transition of the READ pin causes one and only one frame of either rolling reset or rolling read operation before the sensor goes into an "idling" state where only one virtual row is continuously accessed. Another JTAG bit, mode register bit 19, is added for further refinement.

If bit 19 is set to 0, when READ goes from 0 to 1, the complete region of interest (ROI1 if enabled and ROI2) goes through a rolling reset (no data is read). When READ goes to 0, the complete region of interest goes through a rolling data readout. The exposure then is the amount of time that READ is 1.

If bit 19 is set to 1, when READ has a transition, the complete region of interests (ROI1 if enabled and ROI2) goes through a rolling readout with an immediate reset on the same row. The amount of exposure is therefore approximately the duration of the READ pulse. Even though all rows have the same exposure time, the start of exposure differs from row to row. The last row of the frame starts exposure almost a frame time after the rising transition of READ.

TX2 can be used to address the exposure issue described in previous paragraph. When TX2 is asserted, the exposure is held off until the fall of TX2. This means all rows will have the same exposure start time but different exposure end time. This difference may not matter if the light source is pulsed.

# **Timing diagrams**

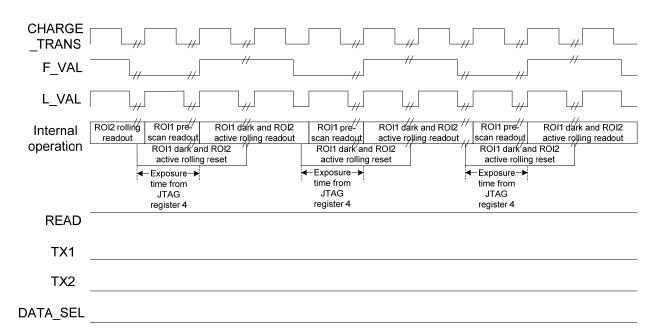

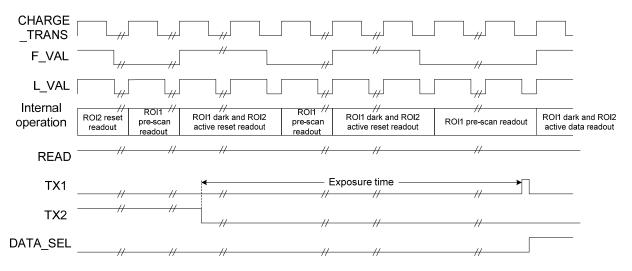

Frame and line timing diagrams of the CIS2521 sensor in various operating modes are shown next.

Figure 14. Basic Rolling Shutter Mode

Figure 16. Basic Global Shutter Mode

**Note:** Figures 17 and 18 show an identical readout mode (Basic Global Shutter Mode) with the only difference being that Figure 17 gives the example of a short exposure time and Figure 18 has a long exposure time.

The signals that are different are F\_VAL (Figure 17 has one Reset frame preceding the Data frame, Figure 18 has two) and TX2 (Figure 17 has TX2 pulsed during the CHARGE\_TRANS low period in each row readout, and Figure 18 has TX2 continuously on or continuously off).

Previously it has been stated that TX2 should be pulsed during the CHARGE\_TRANS low time to avoid banding artifacts in the image. Since the Global Shutter final image is constructed from the Data frame and the immediately preceding Reset frame, any TX2 activity during this immediately preceding Reset frame must be pulsed, and this is shown in Figure 17.

In Figure 18, however, the last falling edge of TX2 is not in the immediately preceding Reset frame (Reset frame 1), but rather in the Reset frame before that (Reset frame 0). TX2 activity in

this region cannot induce any banding artifacts in the final Global Shutter image, since only data in the immediately preceding Reset frame (Reset frame 1) is used to create the final image.

Therefore, pulsing TX2 in Global Shutter is not necessary as long as there is no TX2 activity when active imager rows are being read out for a Data frame or its immediately preceding Reset frame. Having TX2 continuously on during either of these periods would produce banding artifacts. A time period when active imager rows are being read out roughly corresponds to when F\_VAL is high, though F\_VAL is high for both dark rows and active imager rows (= "physical rows"), and F\_VAL (by default) has a 2 row time delay in its rise and fall times from when the physical rows begin and end their frame readout.

Of course, all complications can be avoided by pulsing TX2 during the CHARGE\_TRANS low time regardless of the exposure time. However, pulsing TX2 incurs a cost in current consumption. In Low power applications, TX2 may therefore avoid pulsing for long exposure times, as is shown in Figure 18 below.

Figure 18. Basic Global Shutter Mode, Long Exposure (Similar to Fig 16 but with more details)

Figure 19. Global Shutter Mode using READ pin to extend exposure time

Figures 20, 21, and 22 all use external trigger. In Figure 20, Rolling Shutter exposure is controlled by READ. In Figure 21, Rolling Shutter exposure is controlled by READ and TX2. In Figure 22, Global Shutter exposure is controlled by TX1 and TX2 pulses, as usual, but the timing of Reset and Data frame readouts is controlled by READ.

Figure 21. Rolling Shutter Mode with External Trigger, Reg 2 bit 19=1 and bit 23=1

Note that in Figure 21 there is a transition in TX2 during a CHARGE\_TRANS high period, and in Figure 22 there is a TX1 pulse during a CHARGE\_TRANS high period. Normally this would be forbidden because an artifact might be induced. However, in both cases, the imager is reading out pre-scan rows at these times, and no image artifacts can result during pre-scan readout.

# **Packaging information**

# **Standard Package drawings**

All dimensions are in mm.

Figure 23. Top View of CIS2521 Standard Package

Figure 24. Side View of CIS2521 Standard Package

Figure 25. Bottom View of CIS2521 Standard Package

The standard package has a die placement spec (optical center of die to package center) of  $\pm 4$  mils. The die rotation spec (relative to the package sides) is  $\pm 1^{\circ}$ . The die tilt spec (relative to the package bottom) is  $\pm 1^{\circ}$ .

The thermal pad at the bottom of the package should be grounded.

## **Scientific Package drawings**

All dimensions are in mm.

Figure 26. Top View for CIS2521 Scientific Package

Figure 27. Side View of CIS2521 Scientific Package

Figure 28. Bottom View of CIS2521 Scientific Package

The scientific package has a die placement spec (corners of die to package corner fiducials) of +/- 2.5 mils. The die rotation spec (relative to the package sides) is < 125 microns. The die tilt spec (relative to the package bottom) is < 125 microns.

# Pin list for both Scientific and Standard packages

The CIS2521 image sensor is mounted in a 168-pin ceramic leadless chip carrier (LCC package) for both the Scientific and Standard packages. For both the package types, the pin list is identical. The list shown below provides a complete description of the pin names, their functions and electrical requirements. Note the suffix BT is appended to pins at the bottom of the sensor and the suffix TP is appended to pins at the top of the sensor, the suffix L is appended to pins on left side of the sensor, and the suffix R is appended to pins on right side of the sensor.

| Pin<br>number | Pin name    | Pin<br>type | Signal<br>type | Power requirements (Note 1)                               | Pin Description              |

|---------------|-------------|-------------|----------------|-----------------------------------------------------------|------------------------------|

| 1             | AVDD        | Supply      |                | 3.3v/270mA,<br>Ripple < 1mV<br>RMS                        | AVDD analog supply           |

| 2             | VTX1_NEG_L  | Supply      |                | 0~-1.5v/100mA<br>1μs pulse,<br>Ripple < 100μV<br>RMS      | TX1 negative supply          |

| 3             | AGND        | Ground      |                |                                                           | AGND common ground 0V        |

| 4             | AVDD        | Supply      |                | 3.3v/270mA,<br>Ripple < 1mV<br>RMS                        | AVDD analog supply           |

| 5             | AVDD_RST1_L | Supply      |                | 2.7v-3.0v/1mA,<br>Ripple < 10μV<br>RMS                    | AVDD_RST1 reset supply       |

| 6             | DVDD_3V3_L  | Supply      |                | 3.3v/1mA,<br>Ripple < 1mV<br>RMS                          | 3.3V digital supply          |

| 7             | AVDD_RST2_L | Supply      |                | 2.7v-3.0v/1mA,<br>Ripple < 10μV<br>RMS                    | AVDD_RST2 reset supply       |

| 8             | VTX2_NEG_L  | Supply      |                | +0.8~-<br>1.5v/100mA<br>1µs pulse,<br>Ripple < 1mV<br>RMS | TX2 negative supply          |

| 9             | AVDD_PIX_BT | Supply      |                | 3.3v/25mA,<br>Ripple < 100μV<br>RMS                       | Pixel source follower supply |

| 10            | AGND        | Ground      |                |                                                           | AGND common ground 0V        |

| 11            | AVDD        | Supply      |                | 3.3v/270mA,<br>Ripple < 1mV<br>RMS                        | AVDD analog supply           |

| 12            | AGND        | Ground      |                |                                                           | AGND common ground 0V        |

# **CIS2521F Packaged Part Datasheet**

| Pin<br>number | Pin name | Pin<br>type | Signal<br>type | Power requirements (Note 1)                    | Pin Description                                                                                                                                                                                                                                                                      |

|---------------|----------|-------------|----------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13            | DVDD     | Supply      |                | 1.8v/290mA<br>@287MHz,<br>Ripple < 25mV<br>RMS | DVDD digital core supply                                                                                                                                                                                                                                                             |

| 14            | TX2_BT   | Input       | 1.8v hstl      |                                                | Global TX2 Charge dump control for the bottom imager half. Rise/fall time < 500ns, Skew < 100ns, Ripple < 1mV RMS. (Typically this pin is only used during Global Shutter to provide the "Global TX2" charge dump pulse that marks the beginning of Global Shutter integration.)     |

| 15            | TX1_BT   | Input       | 1.8v hstl      |                                                | Global TX1 Charge transfer control for the bottom imager half. Rise/fall time < 500ns, Skew < 100ns, Ripple < 100µV RMS. (Typically this pin is only used during Global Shutter to provide the "Global TX1" charge transfer pulse that marks the end of Global Shutter integration.) |

| Pin<br>number | Pin name     | Pin<br>type | Signal<br>type | Power requirements (Note 1)                    | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|--------------|-------------|----------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16            | DATA_SEL_BT  | Input       | 1.8v hstl      |                                                | DATA_SEL = 0 selects wavetable A for sensor readout and wavetable B for read/write access. DATA_SEL = 1 selects wavetable B for sensor readout and wavetable A for read/write access.  Typically, for Rolling Shutter operation, wavetable A is always used for sensor readout, so DATA_SEL = 0 (fixed).  For Global Shutter operation, DATA_SEL = 0 selects wavetable A (the GS Reset frame) and DATA_SEL = 1 selects wavetable B (the GS Data frame) so DATA_SEL is constantly switching between 0 and 1. |

| 17            | AGND         | Ground      |                |                                                | AGND common ground 0V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 18            | READ_BT      | Input       | 1.8v hstl      |                                                | External start/pause readout activities control Input                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 19            | DVDD_IO      | Supply      |                | 1.8v/270mA<br>@287MHz,<br>Ripple < 25mV<br>RMS | DVDD digital I/O supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 20            | DVDD         | Supply      |                | 1.8v/290mA<br>@287MHz,<br>Ripple < 25mV<br>RMS | DVDD digital core supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 21            | COUNT_EN1_BT | Output      | 1.8v hstl      |                                                | External count and EXT_VRAMP synchronization Output. Normally ignored unless EXT_VRAMP is being used (which it typically is not).                                                                                                                                                                                                                                                                                                                                                                           |

| 22            | COUNT_EN0_BT | Output      | 1.8v hstl      |                                                | External count and EXT_VRAMP synchronization Output. Normally ignored unless EXT_VRAMP is being used (which it typically is not).                                                                                                                                                                                                                                                                                                                                                                           |

| Pin<br>number | Pin name            | Pin<br>type | Signal<br>type | Power requirements (Note 1)                    | Pin Description                                                                                                                                                                                                                                                                                                                                                       |